FPGA Implementation with Verilog HDL

Program Outcomes

At the completion of the program, learners will be able to:

Design and implement combinational and sequential digital circuits using Verilog HDL, adhering to RTL coding guidelines.

Write synthesizable Verilog code for core digital components including FSMs, counters, and memory elements.

Program and verify FPGA-based implementations to validate digital designs practically.

Design and integrate UART, I2C, and SPI communication protocols using FPGA platforms.

Apply debugging and simulation techniques to identify and fix functional issues in digital systems

Indicative Content

Digital Design

- Introduction to Digital Logic – Boolean Algebra, K-Maps, min-terms, max-terms

- Realization of Logic gates using Mux and Universal Gates, POS, SOP

- Combinational Circuits - Adders, Encoder, Decoder, Multiplexer, DeMultiplexer, Magnitude Comparator

- Sequential Circuits - Latches, Flip-Flops, Counters, Registers

- Finite State Machine - Mealy and Moore FSM, Common FSM coding styles, Sequence detector

- Memory - RAM and ROM

Verilog HDL & FPGA

- Verilog Module

- Data Types

- Operators Modelling Styles

- RTL Coding guidelines

- Continuous assignments

- Procedural blocks

- Sensitivity list

- Blocking and Non-Blocking Statements

- Inter and Intra delay statements

- Race conditions

- Compiler directives

- System tasks

- Arrays Tasks and Functions

Protocols & FPGA

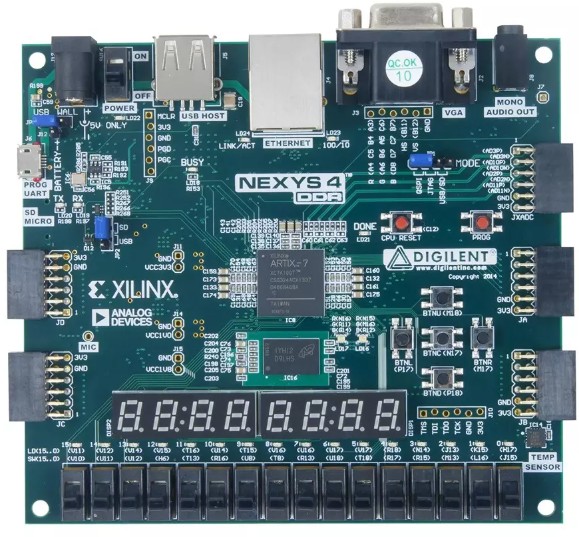

- Introduction to FPGA Architecture & Programming

- RAM & ROM Implementation using FPGA

- UART design and implementation using FPGA

- I2C design and implementation using FPGA

- SPI design and implementation using FPGA